はじめに

過去に PS-PL間の通信帯域やレイテンシを実測して実験していましたが、少しドキュメントから読み取れる仕様についても整理しておきたいと思います。

独自の調査であり、正しく読み取れていない可能性はあるので、誤りはあるかもしれないことを予め申し上げておきます。

先に結論

Read/Write 同時に行えるデバイスは双方向合わせて x2 としてして、DDR4-SDRAMのように Read と Write が交互にしかできないものと区別しています。

マスター側

| width | R/W | MHz | ports | MB/s | |

|---|---|---|---|---|---|

| APU | 128 | 2 | 533 | 1 | 17,056 |

| RPU | 64 | 2 | 500 | 2 | 16,000 |

| GPU | 128 | 2 | 533 | 1 | 17,056 |

| PL(S_AXI_ACP) | 128 | 2 | 333 | 1 | 10,656 |

| PL(S_AXI_ACE | 128 | 2 | 333 | 1 | 10,656 |

| PL(S_AXI_HPC_FPD) | 128 | 2 | 333 | 2 | 21,312 |

| PL(S_AXI_HP_FPD) | 128 | 2 | 333 | 4 | 42,624 |

| PL(S_AXI_LPD) | 128 | 2 | 333 | 1 | 10,656 |

| 合計 | 146,016 |

| MB/s | |

|---|---|

| APU合計 | 17,056 |

| RPU合計 | 16,000 |

| GPU合計 | 17,056 |

| PL合計 | 112,960 |

スレーブ側

| Width | R/W | MHz | Ports | MB/s | |

|---|---|---|---|---|---|

| DDR4-SDRAM | 64 | 1 | 2,133 | 1 | 17,066 |

| OCM | 128 | 2 | 500 | 1 | 16,000 |

| PL ( M_AXI_HPM_FPD) | 128 | 2 | 333 | 2 | 21,312 |

| PL ( M_AXI_HPM_LPD) | 128 | 2 | 333 | 1 | 10,656 |

| MB/s | |

|---|---|

| PL合計 | 31,968 |

調べたこと

バス幅や本数

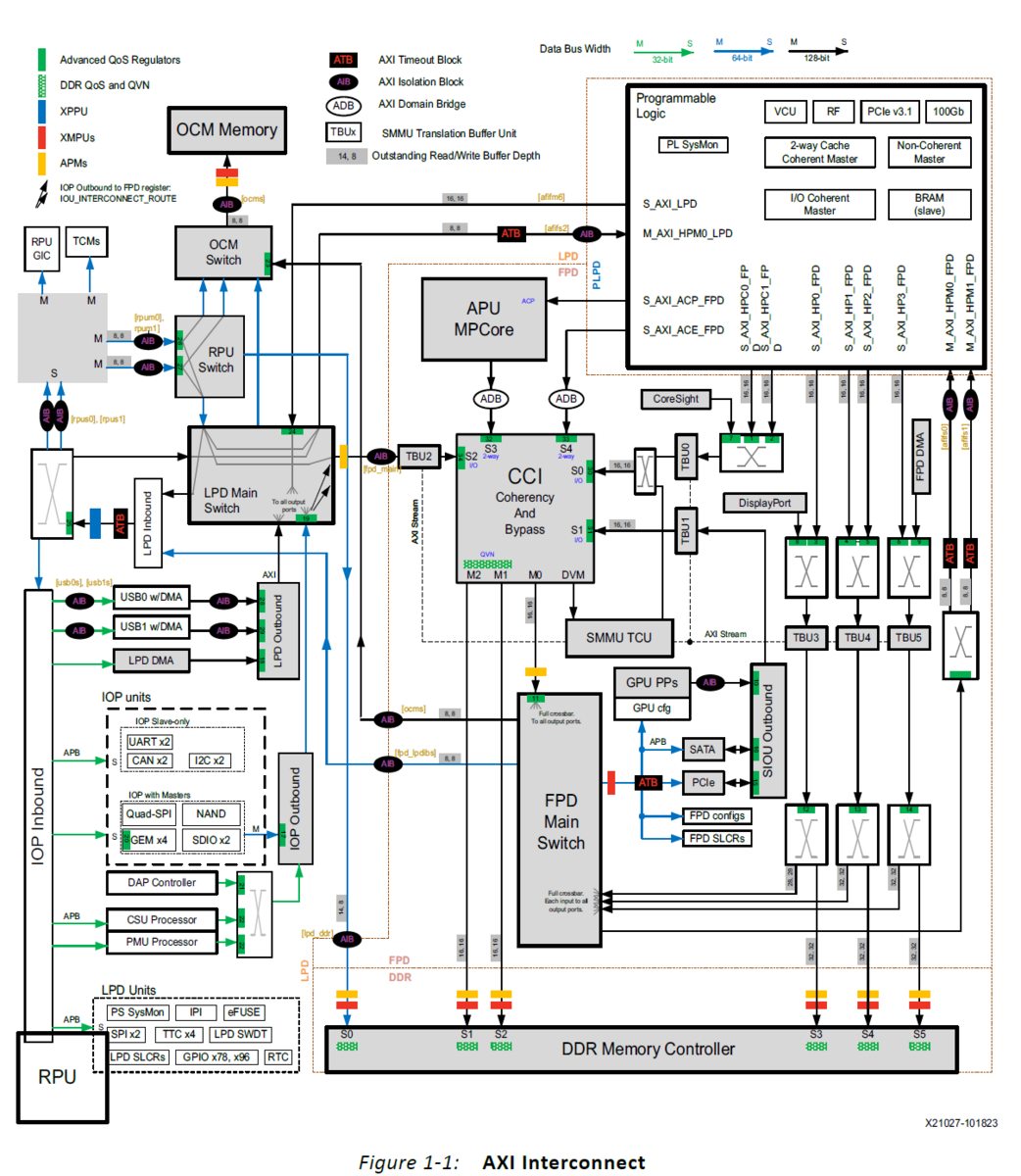

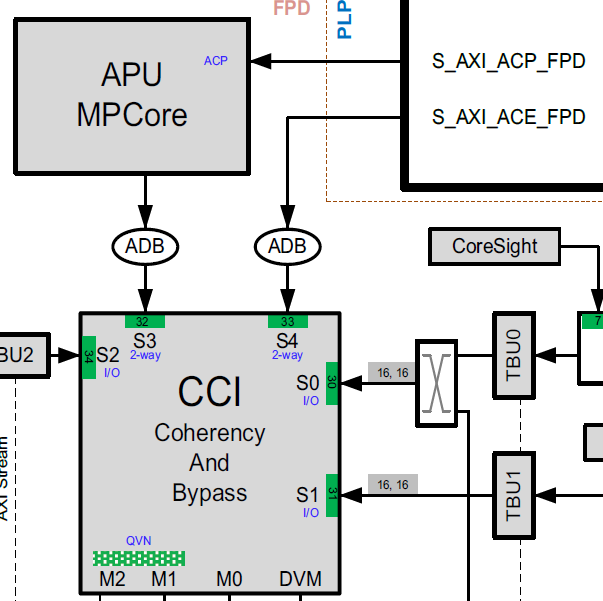

Zynq UltraScale+ Device Technical Reference Manual (UG1085) v2.4 の Figure 1‐1: AXI Interconnect

なぜか pdf 版でないと図がうまく見れなかったのですが、Figure 1‐1に各デバイスに出入りするAXI バスの幅などが記載されています。

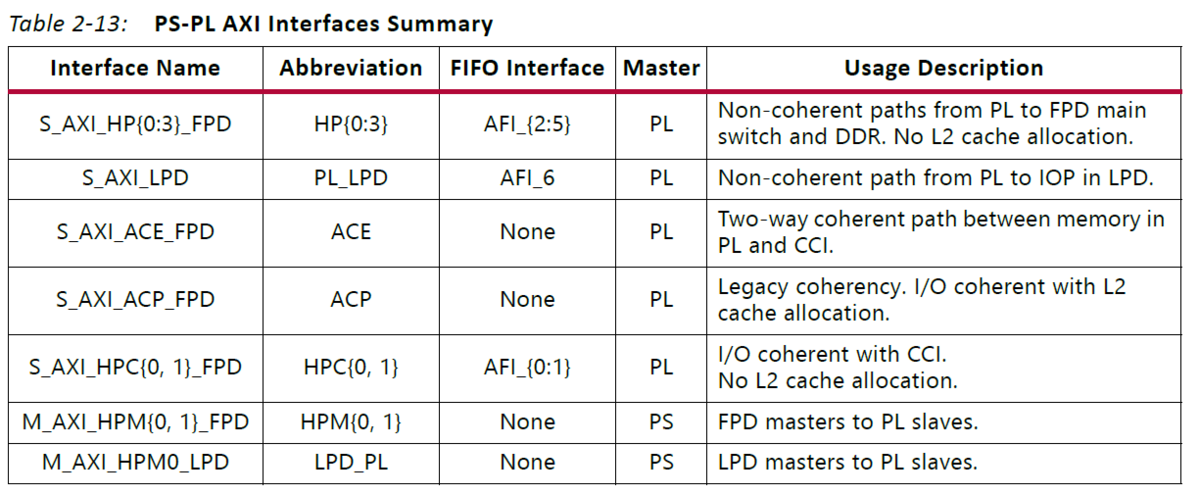

また、キャッシュコヒーレンシを取る部分図中でも 2-way などと記載があるようです。S_AXI_ACE_FPD について 「Two-way coherent path between memory in PL and CCI. 」といった記述がみられます。

周波数

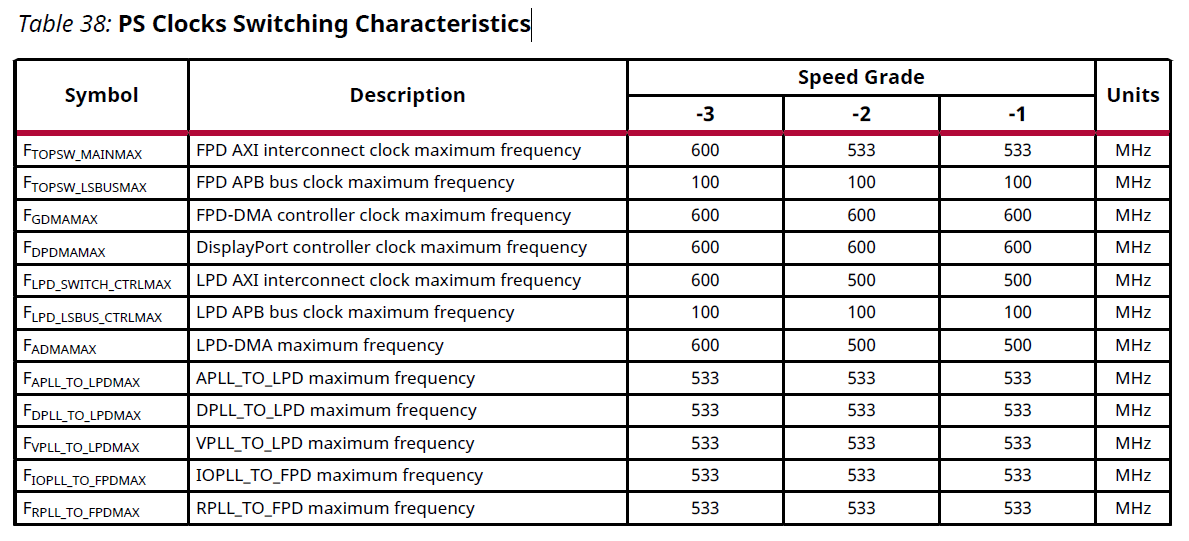

Zynq UltraScale+ MPSoC Data Sheet: DC and AC Switching Characteristics (DS925) v1.27 の Table 38: PS Clocks Switching Characteristics に、周波数の記述があり、スピードグレード -2 の KV260 では

- FPD AXI interconnect clock maximum frequency : 533MHz

- LPD AXI interconnect clock maximum frequency : 500MHz

であることが伺えます。

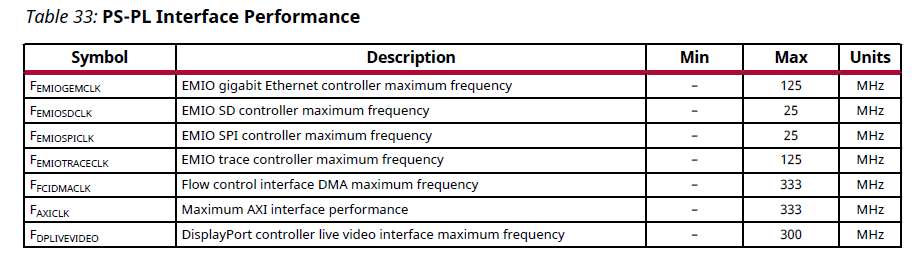

また、下記を見ると PS-PL 間の AXIバスは 333MHz が上限であることが分かります。

DDR4-SDRAM

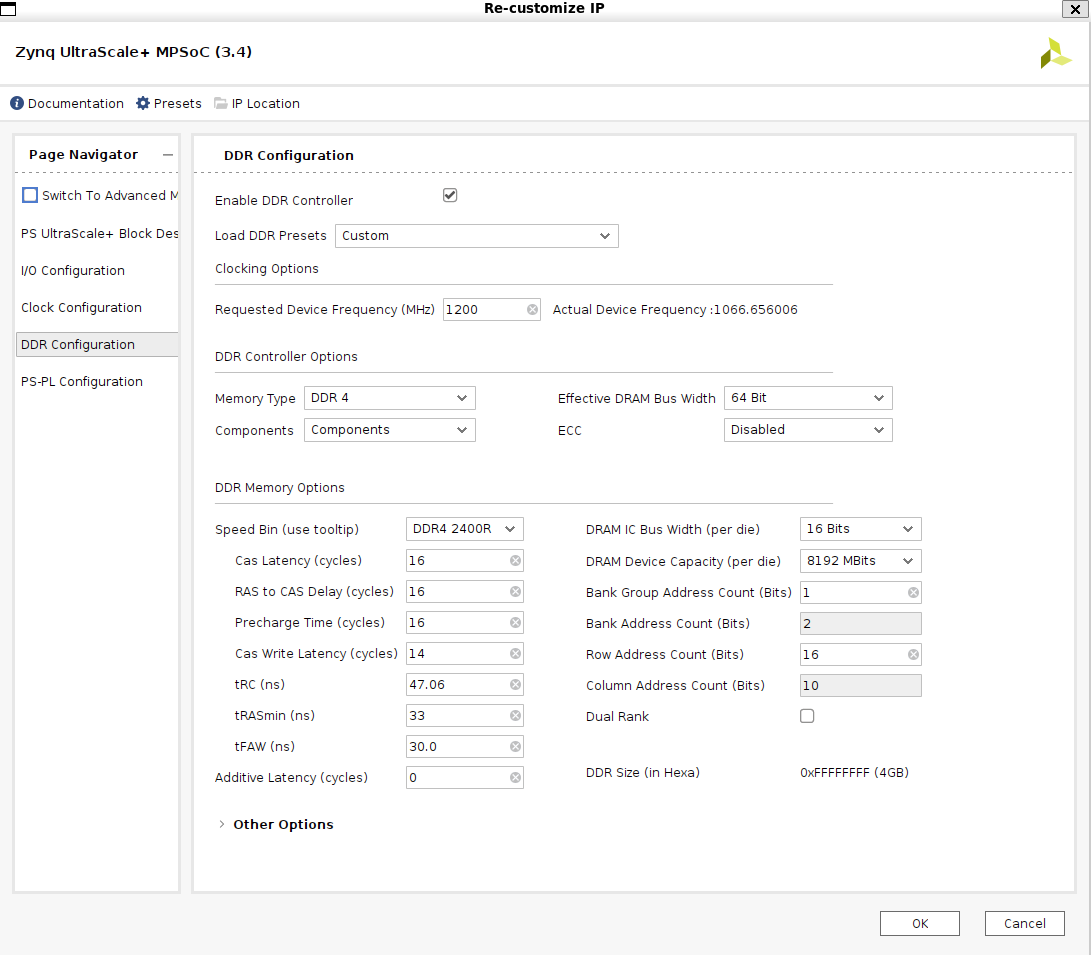

KV260 のボード設定を反映した Zynq コアの設定を覗いてみると バス幅は 64bit で Actual Device Frequency : 1066.656006 という数値が見えます。デュアルエッジ転送でデータレートはこの倍の周波数で 2133MHzとなります。

OCM

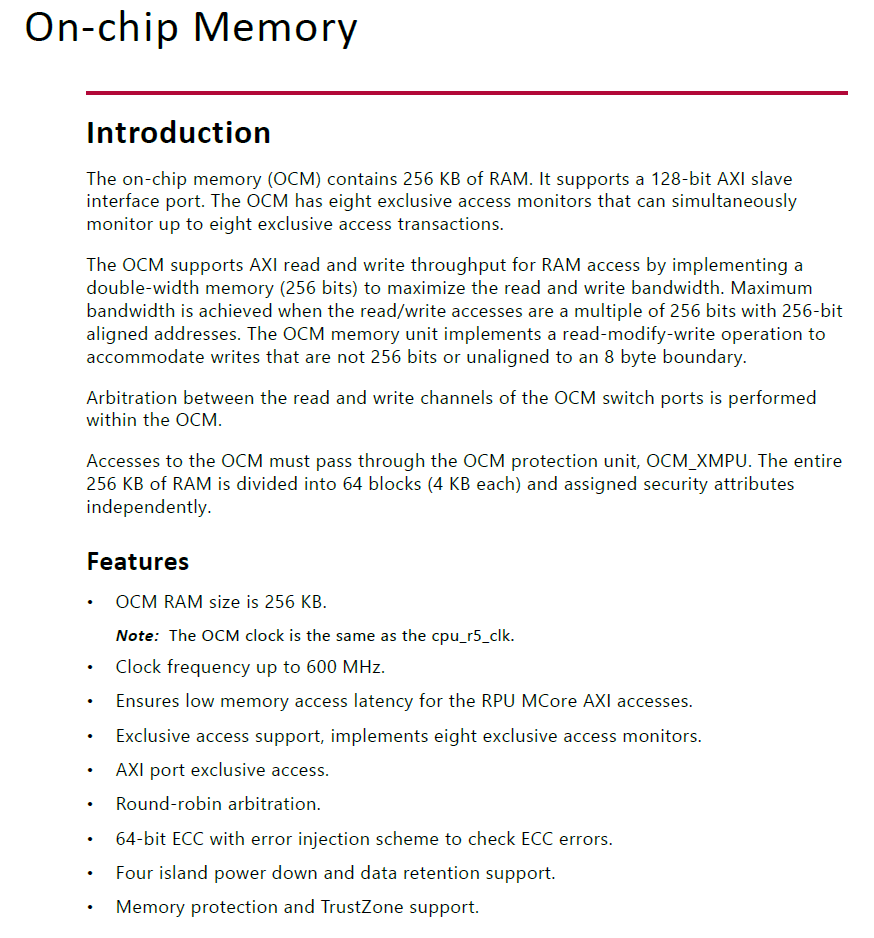

UG1085の On-chip Memory にいろいろと記述があります。

AXIバスは128bit のようですが、メモリは 256bit 幅のようなので、Read/Write 双方向である程度帯域が埋められる仕組みなのではないかと推測しました。

また 「Clock frequency up to 600 MHz.」 と記載がありますが、恐らくスピードグレード -3 の品番の話で、DS925 を見る限り KV260 では 500MHではないかと推測されます。

PL(おまけ)

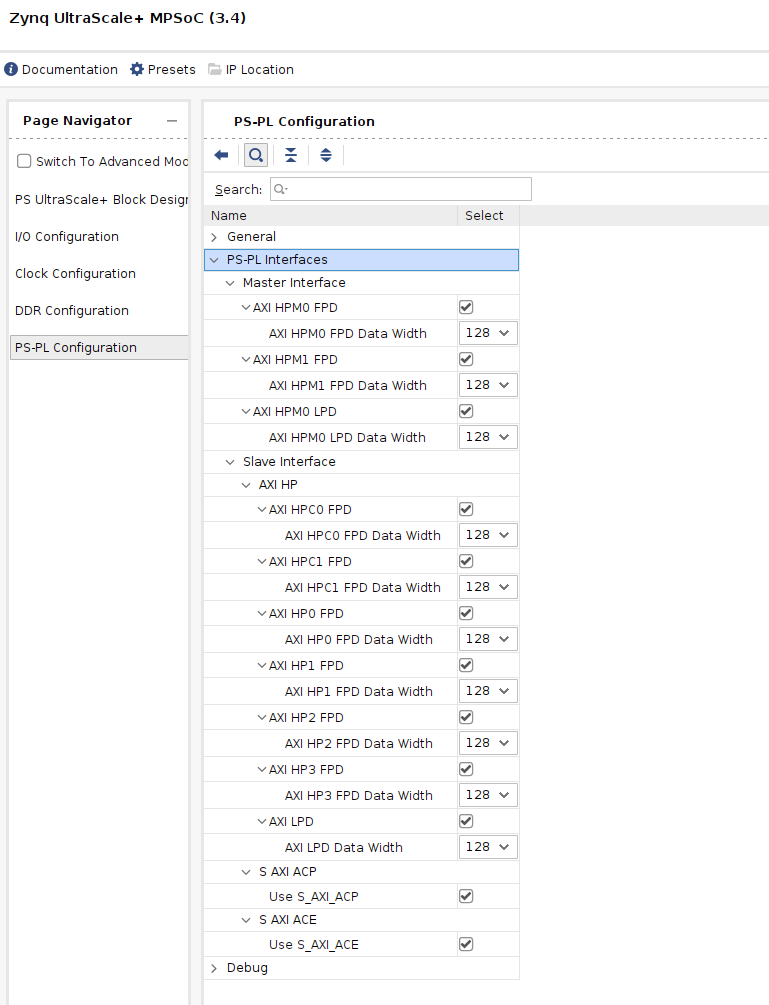

マニュアルからも分かるのですが、GUIでみるとこんな感じです。

APU(おまけ)

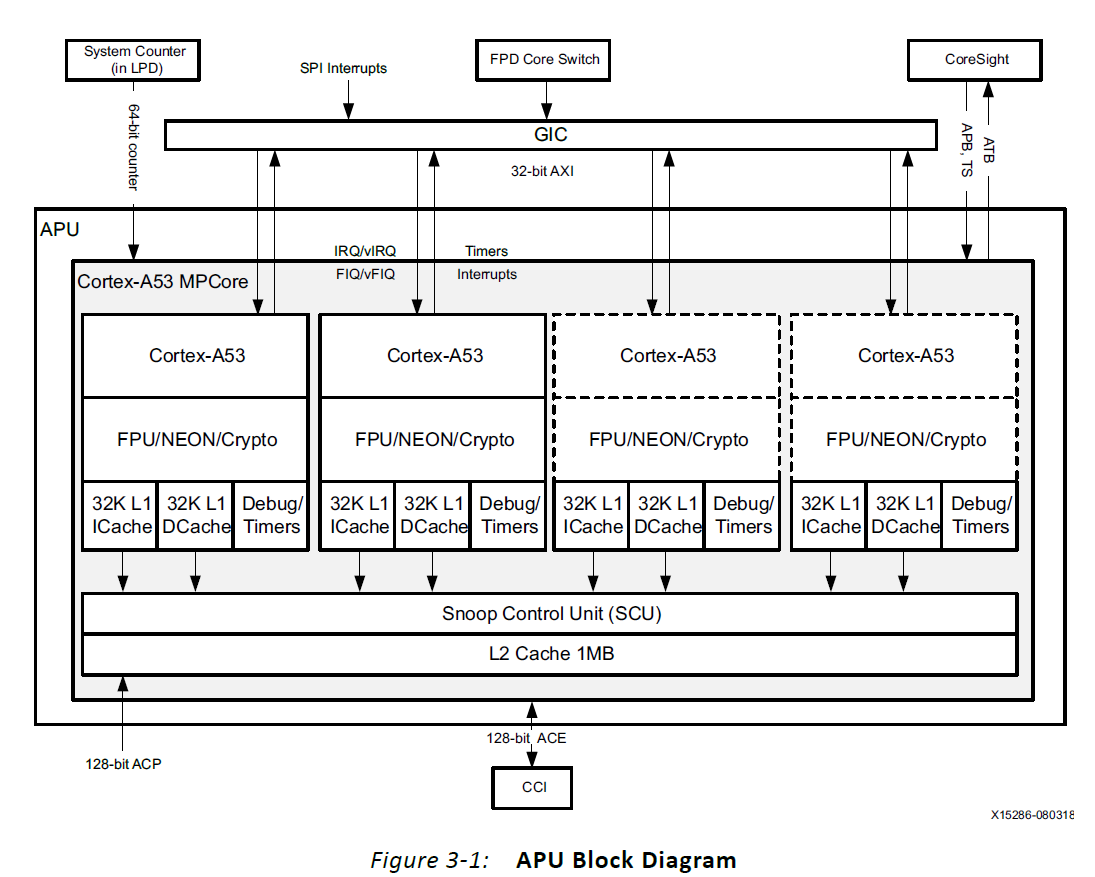

案外 APU の帯域が控えめな気がしましたが、図を見るとやはり 128bit バスが一本出ているだけのようです。

ディスプレイ表示の帯域(おまけ)

私は KV260 に FullHD(1920x1080)@60Hz のモニタを接続していますが、この時のピクセルクロックは 150MHz で 24bit色(3Byte)ですので、ブランキングなどあるにせよ、瞬間最大では 450MB/s の DDR4-SDRAM の帯域が消費されていることになります。

グラフィックカードなどでは専用の VRAM を持ちますが、この手の SoC はいわゆるユニファイドメモリになっているのでこういったところも気にかけておいた方が良いのかもしれません。

おわりに

マニュアルなどをざっと眺めただけではありますが、参考にあれば幸いです。

追記 (2-way) について

ここの部分の 青字の 2-way とかの意味について

ikwzm 様から X でいろいろ教えて頂きました。 X のスレで、私がアホな返信してますが、無視して読んで頂ければ幸いです。

2-way という言葉は初耳ですが ZynqMP の TRM に次のような記載があります。

— 隠居したエンジニア (@ikwzm) 2024年7月15日

> Full Coherency

> Full (both-way) coherent masters can snoop each other's caches.

> I/O Coherency

> The I/O (one-way) coherent masters can snoop APU caches through the CCI ACE-Lite slave ports,...

こんな感じです。 pic.twitter.com/kqJPQs5OuT

— 隠居したエンジニア (@ikwzm) 2024年7月15日

S_AXI_ACE の接続にも 2-way の記述があり、どうやら PL に APU のキャッシュとコヒーレンスを持ったキャッシュを作ることも理屈上は可能だそうです。

- 自身はキャッシュを持たず、他のキャッシュに問い合わせだけしてコヒーレンスを保てるポート(I/O とかの表記部分が 1-way)

- 自身もキャッシュを持ち、自分からの問い合わせだけではなく、他のマスタからの問い合わせにも応答できる (2-way)

という事のようです。勉強になりました。