はじめに

少し前に、HLSで書いたC言語のコードを、コマンドラインから一気に Vivado に取り込んで合成するサンプルを作ってみましたが、ブログにかけてなかったと思うのでこちらにも少し書いておきます。

サンプルはこちらにあります。

とは言え、殆どが下記2つを参考にさせて頂いたので、先人の方々の成果を組み合わせさせて頂いただけという感じではあります。

- https://qiita.com/ikwzm/items/a0120079d2f7f86a5904

- https://kenta11.github.io/2019/02/12/make-for-Vivado-HLS/

なぜこんなことをしたのか

Xilinx の FPGAのツールは、Vitis HLS と Vivado とで分かれています。

ツールの使い方として大きく

- Vivadoでプラットフォームを作った後、高位合成を主体に Vitis で作開発する

- HLSで作ったIPコアをVivadoで利用する

の2種類ありますが、今回は後者にフォーカスしたものです。

この際、「一度作ったHLSのIPコアをめったに弄らない」なら良いのですが、折角の高級言語開発ですので、もっとアジャイルに、「HLS部分もRTL部分もガンガン書き換えながら開発イテレーションを回したい」という思いが出てくるわけです。

その時に異なる2つのツールを跨いで

- HLS で書かれたコードを合成

- 合成した HLS を expoert

- Vivado プロジェクトを生成して HLS を取り込み

- Vivado で全体合成

という手順はとても面倒くさいものですので、コマンドラインから2つのツールを一発で流してしまいたいという思いが発生し、試してみたというものです。

シミュレーションついて

シミュレーションに際して、Verilator と xsim を想定しています。 HLS を使う場合、Xilinx 社の暗号化されたコアが呼び出されるケースがあるのでそういう場合は xsim のみとなるかと思いますが、今回(単なる整数除算)に関しては、運よくそういうコアは使われなかったようで、Verilator でも動きました。

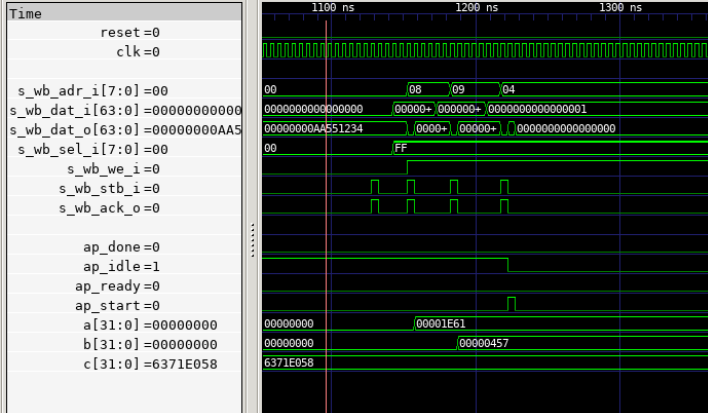

RTLでWISHBONEバス経由でパラメータを設定した後で起動する実験をしてみましたがいい感じで動いている波形が取れました。

そうでない場合は、Verilator を使う場合は、ある程度スタブに置き換えて使っていく必要はあるかと思います。

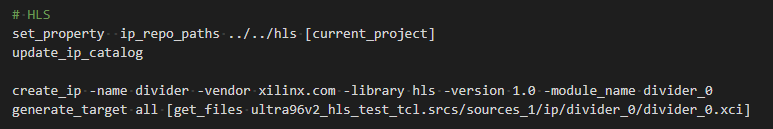

あとは嵌った部分として、Vivado がシミュレーション用のファイルを生成してくれるようにする方法なのですが、tcl スクリプトで下記の generate_target の部分で生成してくれる模様です。

ただこれも出力される場所が、Vivado 2019.2 では .srcs の下に出てくるのに、 Vivado 2021.2 では .gen の下に出てくるなど仕様の差があるようです。

感想とか

今回の作業は、殆どの事はGUIでも当然同じことができますし、GUIであればシミュレーションのファイルがどこにあるかなど気にしなくてもよいなど便利であるのですが、やはりルーティンワークを行うにはコマンドラインが便利には思います。

一方で、シミュレーション周りでは分かり難い部分も多く、tcl という言語自体にあまりなれないこともあって、なんとか動きはしたものの記述もかなり汚いものになっている気はします。 おいおい改善していければと思います。