はじめに

以前こちらに参加させていただいた時に、HPCで演算器を遊ばせないために必要なメモリ帯域や階層キャッシュの容量の話を知る機会があり、エッジコンピューティングの場合どうなのだろう、といろいろと考えておりました。

で、ちょっとだけ構想を Twitter に張ったまま埋まっていたので、埋まり切る前にブログに駄文程度に、張るだけ張っておこうと思います。

リアルタイムコンピューティングのメモリ階層

リアルタイムコンピューティングの場合、基本的には時系列モデルへの適用ですので、状態空間モデルを前提に考えてみました。 正直制御工学はあまり詳しくないのですが、現在の状態を状態変数で表し、離散時間の中で状態を変化させる状態方程式を立式していくようなアルゴリズム開発をイメージしております。IIRフィルタなどもこの部類かと思います。

この時、計算機アーキテクチャ出来には、メモリは過去を覚えておくデバイスになるかと思います。メモリには読み書き速度と容量があり、その性能の違いから階層構造を取る事が多いです。

速度は時間当たりどれだけの密度の情報を記憶できるか、容量はどれだけ昔のことまで覚えておけるかに関わります。

また、メモリはその速度や容量のコストから階層化されることが多いです。FPGAの場合もFFやBRAMのようなデバイス内にある高速アクセス可能なものからDDR4-SDRAMのような大容量だが外部にありアクセスに時間がかかるものまであります。

状態空間モデルにおいて、記憶する内容は状態変数であり、覚えて置ける長さはサンプリング周波数と密接に関わってきます。

さらに、エッジ計算機にはあらゆる速度のセンサーやアクチュエーターが繋がってきます。

という事で、下記が私の持っているイメージです。

計算アーキテクチャを最適化していくには、実際に扱うデバイスに応じて、どのぐらいのサンプリングレートで、どのぐらいの状態変数が持て、どのぐらいの演算ができるのか、と言ったものを考慮してアルゴリズムを考えていくと効率的なシステムにできそうな気がします。

計算機のテクノロジーと言うのは急には増やせませんが、フィットするアルゴリズムを考える事はできます。その時、計算機の中に遊んでいるリソースがあるなら「そこをもっと積極的に使って性能が上げられないか?」というのをアルゴリズム開発段階で考える事が可能になります。

昨今の半導体技術はエッジでも非常に多くのトランジスタを集積可能ですので、案外、「ルールベースではとても使い切れないので、容量余ってるならAI入れてもいいかも」といった帯域もあるかもしれません。

実際のところどうなのか

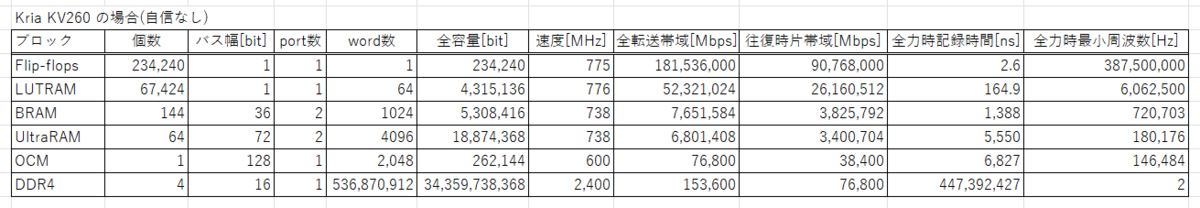

そこで少し実際のデバイスを見てみたいなと思い、発注したままもう当分納品されそうにない(2022/02現在)幻のKV260の場合を調べてみました。

案外書き込み帯域が高く、メモリ全部全力で使った状態空間モデルって結構難しそうに思いました(笑)。

おそらくメモリ帯域が律速することはなく、容量や計算が先に律速しそうです。

その場合、折角のメモリ帯域が遊んでしまいもったいないという事になりますので、よりシンプルな演算で高いサンプリングレート(オーバーサンプリング)で処理するアルゴリズムを考えると今の計算機をもっと効率的に使える気がします。

拙作のLUT-Network も オーバーサンプリングであれこれと言うのは、ずっと試行錯誤してましたので、方向性としては筋は悪くなかったのかもしれません。

なお、深く考察出来てませんので、ほんと思い付きでの駄文までです。